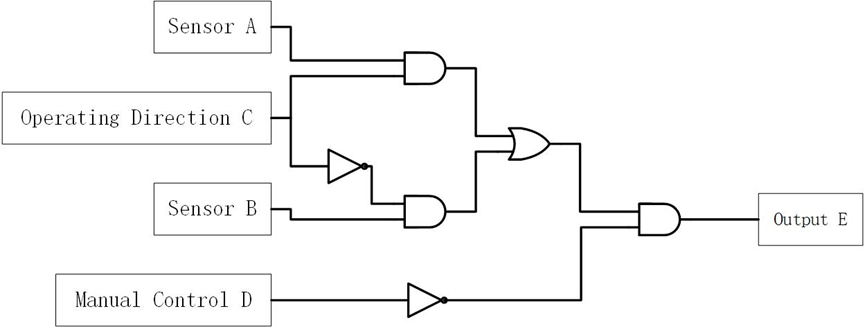

Logic gate description: 3 AND gates, 1 OR gate, and 2 inverters.

Some real-life applications behind the circuit:

The circuit should be able to tell the escalator power system if it should generate full power to keep the escalator running. When there are no people using the escalator, the electric motor will run in a slower speed only to maintain the basic function. However, if heavy human traffic is detected, the escalator should run at full speed. Also, a manual override key should be included to determine whether the energy saving system should work in case of special requirements.

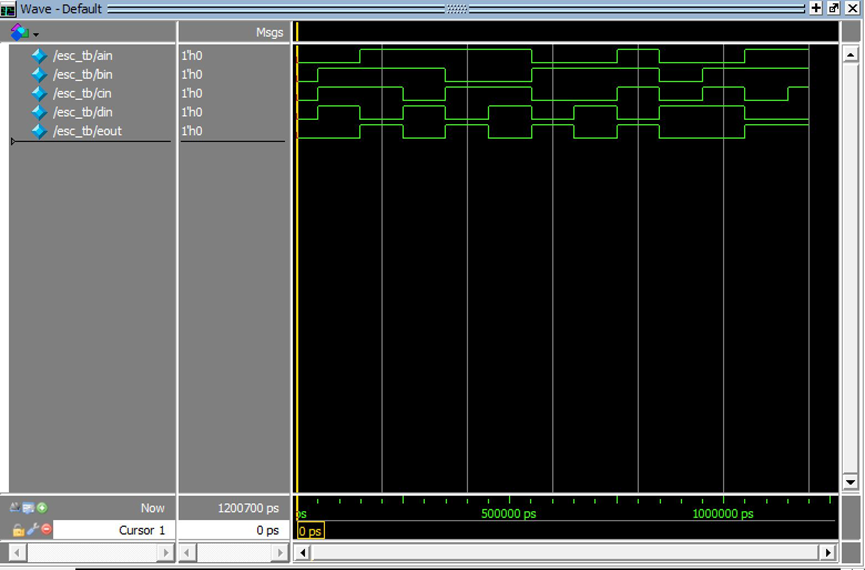

Running in Modelsim simulation, the timing diagram is shown below:

PS: The testbench uses random%2 function to generate random 1 or 0 data flow, your simulation result can be different from mine.

Verilog files (testbench included) can be found below. If you are interested in my waveform, feel free to open my wave file and check the result : )

Good day I am so grateful I found your website,

I really found you by error, while I was researching on Bing for something else, Regardless I am here

now and would just like to say thank you for a remarkable post and a all round enjoyable blog (I also love the theme/design), I don’t have time to look

over it all at the moment but I have bookmarked it and also added your RSS feeds,

so when I have time I will be back to read much more, Please do keep up

the superb b.